一种从根本上减少了任何NeRF模型必须执行的工作量,另一种则消除了不规则的DRAM访问

(中国AI网 2024年10月28日)神经辐射场NeRF是传统的基物渲染的替代方案。然而,NeRF尚未在虚拟现实和增强现实等资源有限的移动系统中得到应用,这是因为它的速度非常慢。在移动Volta GPU,即便是最先进的NeRF模型通常都只能以0.8 FPS执行。

在一项研究中,上海交大和罗切斯特大学展示了主要的性能瓶颈是算法和架构,并引入CICERO。他们首先介绍了两种算法,一种从根本上减少了任何NeRF模型必须执行的工作量,另一种则消除了不规则的DRAM访问。然后,团队描述了一种消除SRAM组冲突的片上数据布局策略。

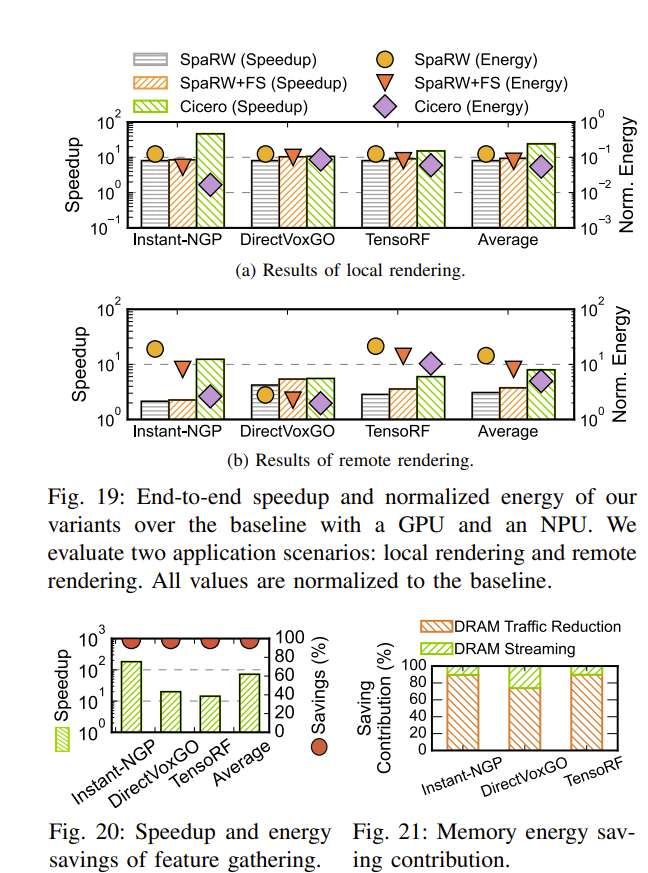

CICERO的纯软件实现比移动Volta GPU提供了8.0倍的加速和7.9倍的节能。与专用DNN加速器的基线相比,加速和能量减少分别增加到28.2倍和37.8倍,而所有这一切都只涉及最小的质量损失(峰值信噪比降低小于1.0 dB)。

神经辐射场NeRF使用现代深度学习技术恢复了经典的基于图像的渲染,并已成为传统的真实感渲染方法的一种前景替代方案。然而,NeRF太慢。尽管做出了很多努力,但在AR/VR等移动设备端,NeRF渲染的实时性依然很差。在移动Volta GPU,像DirectVoxGO这样的常见模型只能达到每秒0.8帧,而Instant-NGP需要超过6秒才能渲染800 × 800帧。

加速NeRF模型至关重要,但由于算法设计的快速发展,人们不能过分专注于特定的模型。NeRF模型经历了几次主要的架构变化,从最初的基于网格/体素的设计到使用分层数据结构的设计,以及最近通过高斯飞溅的基点渲染。可以想象,NeRF模型依然需要经历更多的迭代才能成熟。

因此,任何系统和架构支持都必须解决神经渲染的核心瓶颈。团队确定了NeRF模型在算法设计和底层硬件方面的固有瓶颈。在算法方面,NeRF模型必须计算数百万条射线的亮度,而每条射线都携带数百条射线样本。

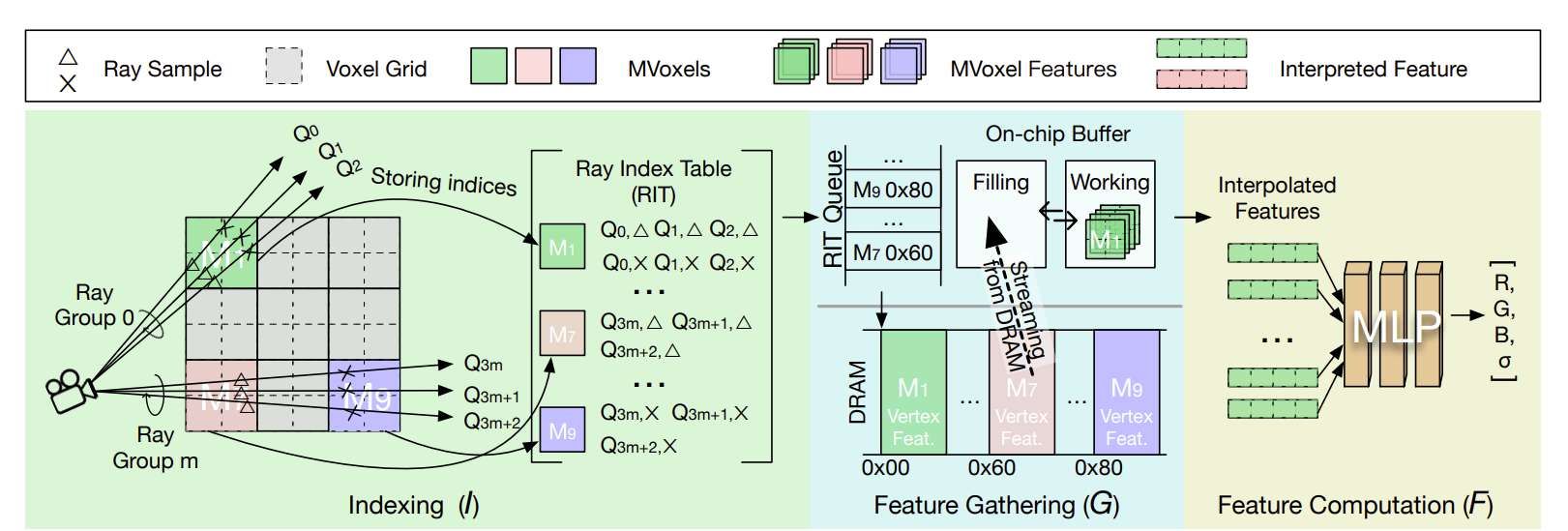

每个射线样本执行一个多层感知器MLP推理,共同产生很高的计算成本。从架构上讲,MLP的实际计算引入了不规则的内存访问,这源于在NeRF中对射线样本进行分组和访问的方式。因此,NeRF渲染导致许多不规则的DRAM访问和SRAM组冲突。

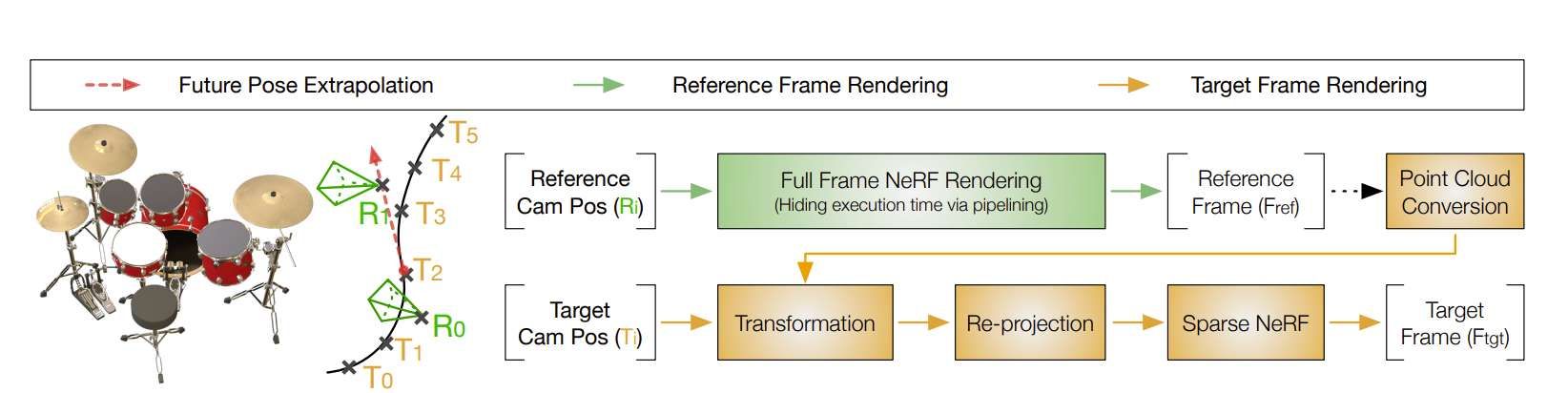

研究人员提出了一种算法架构协同设计的方法CICERO。在算法方面,引入对现有NeRF算法的即插即用扩展,从根本上减少了NeRF模型的计算工作量。特别是,团队利用了辐射接近性:从同一物理点发出的附近射线的辐射度大致相同。

他们提出了稀疏辐射扭曲SPARW,通过重复使用前一帧计算的射线辐射来避免高达88%的辐射计算。关键是,SPARW不是一个新的NeRF模型。相反,它是一种扩展,可以很容易地集成到几乎所有现有的NeRF方法中,从而扩大了其适用性。

尽管SPARW避免了很大一部分辐射计算,但SPARW并没有完全消除它。当需要进行辐射计算时,DRAM访问不规范和片内SRAM组冲突频繁成为瓶颈。

团队进一步提出了两种优化技术来缓解内存在辐射计算中的低效率。为了消除不规则的DRAM访问,研究人员将NeRF推理从以像素为中心的顺序转换为以内存为中心的顺序。

以像素为中心的渲染遵循光线(最终是图像像素)及其样本的顺序,导致不连续的内存访问。相反,以内存为中心的顺序依次访问场景中的体素,固有地产生全流内存访问。

为了消除SRAM组冲突,在片上SRAM中探索了一种新的数据布局策略。传统的特征主数据布局将一个特征向量的所有通道分配到同一个SRAM组中,这必然会导致频繁的SRAM组冲突。

相反,团队提出了一种通道主布局,其中相同特征向量的不同通道分布在SRAM组中。通过共同设计的硬件架构,新的数据布局可以完全消除片内组冲突。

相关论文:Cicero: Addressing Algorithmic and Architectural Bottlenecks in Neural Rendering by Radiance Warping and Memory Optimizations

总的来说,他们将CICERO与三种最先进的NeRF模型集成在一起。纯软件实现比移动Volta GPU实现了8.0倍的加速和7.9倍的节能。另外,与专用DNN加速器的基线相比,加速和能量减少分别增加到28.2倍和37.8倍。

通过扭曲前一帧计算的辐射,以小于1 dB的PSNR损失,减少了NeRF中95%以上的MLP计算。实验同时表明,将NeRF推理从以射线为中心的顺序转换为以场景为中心的顺序,可以实现完全顺序的DRAM访问。

最后,研究人员证明了以通道为主而不是以特征为主的顺序放置特征向量可以消除片上SRAM组冲突。概括而言,所述解决方案在移动Volta GPU展示了一个数量级的加速和节能。